# Design and Analysis of High Performance Operational Transconductance Amplifier

Reetesh V. Golhar, Mahendra A. Gaikwad, Vrushali G. Nasre

Bapurao Deshmukh college of Engineering, sevagram, Maharashtra, India

Abstract- This paper presents a high performance Operational Transconductance Amplifier (OTA) that combines two linearization techniques, and one gain enhancement technique. The two linearization technique are adaptive biasing of differential pairs and resistive source degeneration. The gain enhancement technique is Comman mode feedback Amplifier. The Operational Transconductance Amplifier has ±0.9v power supply. Operational Transconductance Amplifier has been simulated with TANNER 0.18µm CMOS technology in Tspice. The simulated third order harmonic distortion (HD3) with applying a 300mvP-P differential input, remains below -60dB at 3MHz frequency, also the simulation result gives Transconductance gain(gm) 5.247mA/V for 10mV(p-p) input voltage.

*Index Terms*- Operational Transconductance Amplifier (OTA); linearity; adaptive bias circuit; source degeneration; CMFB circuit.

# I. INTRODUCTION

Operational Transconductance Amplifier (OTA) is a fundamental building block of analog circuits and systems. OTA has been used to implement many kinds of analog circuits such as; opamps, data converters, four-quadrant multipliers, mixers, modulators and continuous-time filters [1]-[10]. In such application as asymmetrical digital subscriber lines (ADSL) and cable-modem, the linearity has to be 60dB while for example, video applications require at least 60dB of linearity at 5MHz [5]. Gm-C topology is a good choice for realizing continuous-time filter has better performance in frequency response and electronic tuning capability, but suffer from poor linearity[5]-[8]. Thus designing an OTA with high linearity and high Trasnsconductance gain tends to be a constraint in circuits and systems design task.

In literatures several techniques have been presented to design Operational Transconductance Amplifier to achive gain Transconductance well as as Linearity. Transconductance gain has been improved by using three stage amplifier circuit. In [3] utilizing a tail current depends on the square of input differential signal, linearity in output current of strong inversion transconductor has been improved. This technique which is known as adaptive bias technique loses its performance due to second order effects in modern nano scale devices. Source/gate degeneration is another technique for linearity enhancement, specially in nano scale CMOS technology which the HD3 due to mobility reduction effect is considerable [2]. Some other techniques use two or multiple Gm cell to cancel

third order harmonic distortion [4]-[9]. Double Differentia Pair (DDP) is one of these techniques that uses two cross coupled differential pairs. Then choosing proper sizing and tail current biases can cancel the third order harmonic. The main drawback of these techniques is higher power consumption and transconductance loss [4].

1

In this paper we combine adaptive bias [12], source degeneration techniques and Common Mode Feedback circuit to improve the linearity and Transconductance gain of a OTA. A well accurate-precise analog processing requires a pure wanted signal. This means that the required signal is distortion free and interference free (common mode signal). Consequently to ensure the best processing condition high linear signal, the point which seems to be less regarded in most works so far. Therefore in this work the Improved adaptive bias circuit and common mode feedback circuit is used to provide a high linearity and high gain. In section II we propose the principle and theoretical relations of these linearization techniques. In section III complete linear OTA and theoretical relation for high Transconductance gain is shown. In section IV simulation results are given and in section V we conclude the paper.

## II. PRINCIPLE OF LINEAR TRANSCONDUCTOR

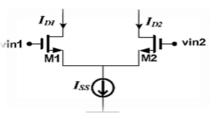

Fig. 1 shows a source-coupled n-channel differential pair that is biased by current tail *ISS*. In this figure *vin1* and *vin2* are input signals including both common and differential modes. The large-signal i-v transfer characteristic will be given by:

$$\begin{split} & Iout = I_{D1} - I_{D2} = \frac{1}{2} \frac{1}{\beta \text{vin}} \sqrt{\frac{4I \text{SS}}{\beta}} - \text{vin}^2 \\ & I_{D1} - I_{D2} = I_{ss} \text{ sgn}(\text{vin}) \\ & \beta = \mu_n \, c_{ox} \frac{\underline{\nu}}{L}, \quad v_{in} = v_{in1} - v_{in2} \end{split} \quad |V_{in}| > \sqrt{\frac{2I \text{SS}}{\beta}} - (1 - a)$$

Figure 1: Simple differential pair.

In (1) vin is differential input (vin1-vin2) and "sgn" is sign function. Other parameters in (1) have their usual meanings. For

realizing a linear relation between differential output current and differential input voltage, the result of radical in (1-a) should be a constant. This will be realized using a tail current containing a component dependent on the quadratic input  $\emph{vin}^2$  to cancel the nonlinearity of the output current. So assuming  $I_{ss} = I_{ss0} + k' V_{in}^2$  we get:

$$Iout = \frac{1}{2} \frac{W}{\mu_n c_{ox}} \sqrt{\frac{4Iss0}{\beta \mu_n cox W/L} + (\frac{4k'}{\mu_n cox W/L} - 1)}$$

(2)

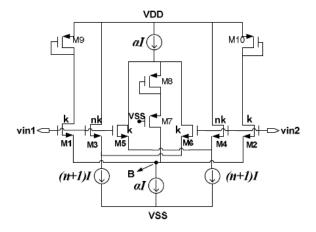

In [12] biasing current, dependent to input signal has been implemented with cross coupled differential pair biased by constant separate current source. Fig. 2 shows the improved adaptive biased transconductor. In Fig. 2, the currents of M5, M6 transistors can be expressed as follows [4]:

$$I_{5}=I+I\left[Y(V_{in}\sqrt{K/I})^{2}+\frac{x}{2}(V_{in}\sqrt{K/I}\sqrt{1-\eta(Vin\sqrt{K/I})2}\right]_{(3-a)}$$

$$I_{S}=I+I\left[Y(V_{in}\sqrt{K/I})^{2}+\frac{\kappa}{2}(V_{in}\sqrt{K/I}\sqrt{1-\eta(Vin\sqrt{K/I})2}\right]_{(3-b)}$$

Where,

$$x = 4n/(n+1), c^{\eta} = n/(n+1)^2, Y = n(n-1)/(n+1)^2$$

$$K = \frac{1}{2} \mu_n c_{ox} \frac{W}{L} \tag{4}$$

Sum of these currents depends on the quadratic input  $vin^2$

As:

$$15 + 16 = 2I + 2I \left[ -Y(V_{in}\sqrt{K/I})^{2} \right] =$$

$2I + \left[ 2n(n-1)/(n+1)^{2} KV_{in}^{2} \right]$  (5)

Which is the same as  $I_{ss} = I_{ss0} + k'V_{in}^2$  if

$$K' = \left[2n(n-1)/(n+1)^2\right] K$$

To remove the nonlinearity in (2)

we should have [5]:

$$\frac{4k'}{\mu n \cos W/L} - 1 = 0 \Longrightarrow \frac{2k\nu}{k} - 1 = 0 \Longrightarrow k' = \frac{k}{2}, n = 2.155$$

(6)

Figure 2: Improved version of adaptive biased transconductor

For short channel devices the effective carrier mobility is a function of both the longitudinal and transversal electric fields. Considering the degradation of mobility due to these effects the drain current of a transistor in saturation region can be approximated as [11]:

$$I = \frac{k(VGS - Vth)^2}{1 + \theta(VGS - Vth)} (1 + \lambda VDS)$$

(7)

Where,  $\theta$  is the mobility reduction factor. From (7) The effect of  $\theta$  can be interpreted as the use of a degeneration resistance of value  $R^{\theta} \square \square^{\theta} \square \square^{\theta} \square \square^{\varrho}$  connected to source terminal. In Fig. 2, mobility reduction effect results in a tail current which depends also on forth power of input signal as equation (8)[12].

$$I_{ss} = I_{ss0} + k' V_{in}^{2} + k'^{3} Req^{2} V_{in}^{4}$$

$$Req = \frac{\theta n}{2kn} \frac{\theta p}{2kp}$$

(8)

Equation (8) shows that mobility reduction effect degrades the capability of adaptive bias technique in linearity improvement. Thus, for linearity improvement in this work, we use both adaptive bias and source degeneration techniques. For simplicity we investigate the effect of source degeneration technique for decreasing HD3 in a simple differential pair. Ignoring second order effect, the output current of Fig. 1 can be described by a Taylor series expansion as follows:

$$i_{out} = ID1 - ID2 = \sum_{n=0}^{\infty} GM, (2n+1)vin^{2n+1}$$

(9)

Where, GMs are the coefficients of odd powers of the differential input voltage. Considering mobility degradation effect we will have:

$$GM, l = \frac{1}{2} \frac{\sqrt{kp(\frac{W}{L})Iss}}{1 + \frac{2}{\epsilon crit}\sqrt{Iss/WLK_F}}$$

(10-a)

$$GM,3 = -\frac{GM,1}{8\left(\frac{Izz L}{2Kp W}\right)\left(1 + \frac{2}{\varepsilon crit}\sqrt{Iss/WLKp}\right)3}$$

(10-b)

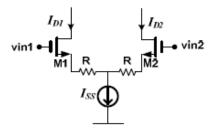

Where  $K_p$  is a technological parameter, *ecrit* is the critical electric field, W is the width and L is the length of the transistors[5]. If two source degeneration resistors be added as shown in Fig. 3, the ac components of the output approximately becomes:

$$iout = \frac{GM,1}{(1+GM,1R)}vin + \frac{1GM,3}{(1+GM,1R)} vin^3$$

(11)

Relation (11) shows that HD3 is decreased by 1 ( $1 \square N r \square$ )3, where  $Nr \square \square GM$ , 1R. Using this topology for source degeneration (two resistors that current tail is in middle of them) has lower input referred voltage noise.

## III. PROPOSED OTA

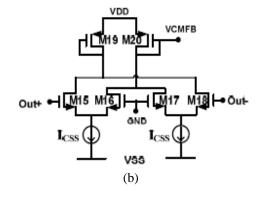

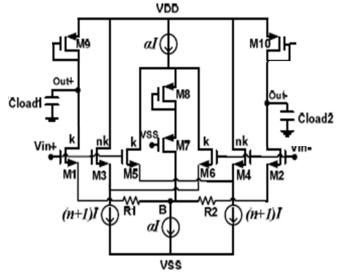

With reference to principles explained in section II the complete fully differential OTA which benefits from the source degeneration and adaptive bias techniques as well as a CMFB circuit shown in Fig. 4.

In this circuit  $\alpha$ =4, n=2.16, I=20 $\mu$ A and ICSS=10 $\mu$ A. To avoid from drawbacks associated with resistive source degeneration which mentioned before, small resistors (R=210 $\Omega$ ) is used. The CMFB circuit sense the CM level of the two outputs and accordingly adjust one of the bias current in Operational Transconductance Amplifier.

From fig. 4

$$\beta$$

is closed loop feedback factor.

$$\beta = \frac{v_{out} + v_{out}}{v_{out} - v_{out}} iout = 0$$

(12)

$\beta = -(gm13 + gm14)(Ron13 || Ron14)$

$$\beta = 2\mu_n c_{ox} \left(\frac{w}{L}\right)_{13,14} \frac{1}{(2\mu n \cos(\frac{w}{L})13,14),(VG513,14-VTH13,14)}$$

$$\beta = \frac{VD513,14}{(VG513,14-VTH13,14)}$$

where  $VGS_{13,14}$ - $VTH_{13,14}$  denotes the overdrive voltage of  $M_{13}$

and

$$M_{14}$$

. Thus

$$\begin{vmatrix} dVout,CMFB \\ dVb \end{vmatrix} = \frac{VGS13,14-VTH13,14}{VDS13,14}$$

Since  $VGS_{13.14}$  (i.e. the output CMFB) is typically in the vicinity of VDD/2, The above eq. suggest that VDS<sub>13,14</sub> must be maximized.

Figure 3: Source degeneration for linearity enhancement.

Figure 4 (a) Proposed linear OTA. (b) CMFB circuit

The simulation result show that improved version of adaptive bias circuit and source degeneration circuit provide linearity with coefficient of corelation  $(r^2) = .9894$ .

## IV. SIMULATION RESULTS

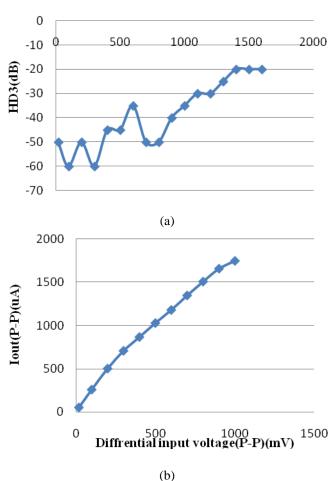

The proposed OTA (Fig. 4(a)) have been simulated using the standard 0.18µm CMOS technology in Tspice simulator. Power supply of the circuit is  $\pm 0.9v$ . Applying an input signal with frequency near to unity gain frequency (3MHz), HD3 of output current in capacitance loads versus magnitude of input signal with source degeneration and adaptive bias technique is shown In fig. 6-a. The value of peak-to-peak differential current in capacitance load (iCload1-iCload2) is also shown in fig. 6-b.

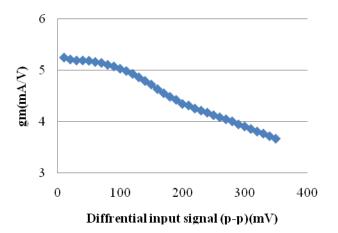

Fig. 7 shows transconducance gain versus differential input signal that verifies the minimum difference voltage gives high gain. Table I shows the main specifications of proposed OTA compared with some similar works.

## Diffrential input voltage (P-P)(mV)

Figure 6: (a) HD3 of output current using adaptive bias technique and source degeneration with  $R=210\Omega$ . (b) Peak to Peak differential output current which gives coefficient of correlation(r2) = .9892.

Figure 7: Transconductance gain versus differential input signal.

Table I. Specifications of Proposed OTA Compared With Similar Works.

| Specification  | This   | [15]   | [9]    | [10]   |

|----------------|--------|--------|--------|--------|

|                | work   |        |        |        |

| Technology     | 0.18um | 0.18um | 0.18um | 0.18um |

| Supply voltage | 0.9V   | 1V     | 1.8V   | 1.1V   |

|                |        |        |        |        |

| DC gain        | 45dB   | NA     | NA     | 63dB   |

| Transconductan | 5.247m | 100 u  | 20 u   | NA     |

| ce gain(gm)    | A/V    | A/V    | A/V    |        |

| Linearity      | HD3= - | HD3= - | HD3= - | THD= - |

|                | 60 dB  | 55dB   | 65 dB  | 62 dB  |

|                | 0.3Vp- | 0.7Vp- | 0.6Vp- | 1Vp-p  |

|                | p at   | p at   | p at   | at     |

|                | 3MHz   | 30MHz  | 1MHz   | 100KH  |

|                |        |        |        | Z      |

## V. CONCLUSION

In this paper we proposed a highly linear OTA which combines two linearization techniques and one gain enhancement technique. An improved Adaptive bias circuitry and source degeneration with low resistance (210 $\Omega$ ) is utilized to improve the linearity in nano scale CMOS technology. Using small resistors makes this circuit suitable for low voltage low-power application. OTA has been simulated with 0.18 $\mu$ m CMOS technology in Tspice. The simulated third order harmonic distortion (HD3) with a 300mvP-P differential input remains below -60dB for frequency up to 3MHz which gives coefficient of correlation( $r^2$ ) = .9892 also the simulation result gives Transconductance gain(gm) 5.247mA/V for 10mV(p-p) input voltage.

#### REFERENCES

- [1] Farzan Rezaei, Seyed javad azhari "A Highly Linear Operational Transconductance Amplifier(OTA) With High Common Mode Rejection Ratio "Iran University of scienc Technology Tehran, Iran.-2011

- [2] Majid Memarian Sorkhabi, Siroos Toofan "Design and simulation of High performance Operational Transconductance Amplifier "canadian Journal on Electrical and Electronics Engineering Vol.2 No july 2011

- [3] Tsung-Hsien Lin, Chin-Kung Wu, and Ming-Chung Tsai "A 0.8V, 0.25mW Current-Mirro OTA with 160-MHz GBW in 0.18um CMOS " *IEEE transactions on circuits and systems* vol.54 no. 2 February 2007.

- [4] Slawomir Koziel, Stanislaw Szczepanski, "Design of Highly LinearTunable CMOS OTA for Continuous-Time Filters," *IEEE Trans Circuits Syst.*, vol. 49, no. 2, Feb. 2002

- [5] Abhinav Kranti, G. Alastair Armstrong "Nonclassical Channel design in MOSFETs for improving OTA gain-Bandwidth Trade-off" IEEE transactions on circuits and systems vol.55 no. 4 January 2011.FLEXChip Signal Processor (MC68175/D), Motorola, 1996.

- [6] Doo-Hwan Kim, Kyoung-Rock Cho "CMOS OTA Compensating Transconductanc linearity with PMOS path" Dept. of Information and Communication Eng. CBITRC chungbuk National University Cheongiu, Korea-2008.

- [7] A. Lewinski, J. Silva-Martinez, "A High-Frequency Transconductor Using a Robust Nonlinearity Cancellation," in IEEE Trans. Circuits Syst. II: Expr. Briefs, VOL. 53, NO. 9, Sep. 2006

- [8] Y. Yussof, R. Musa, "A High-Gain and High-Speed OTA for 10-bit 50MS/s Pipelined ADC," in Proceedings of 2008 Student Conference on Research and Development (SCOReD 2008) 26-27 Nov. 2008, Johor, Malaysia

- [9] Tien -Yu Lo, Chung-Chih Hung, "A 1-V 50-MHZ Pseudo-diffrential OTA with compensation of the Mobility Reduction," *IEEE J. Solid State Circuits*, vol 54, no. 12, Des.2007

- [10] I.S.Han, "A novel tunable transconductance amplifier based on Voltage contrilled resistance by MOS transistors," *IEEE Trans. Circuits Syst. II Exp. Briefs*, vol 53, no.8, pp. 662-666, Aug-2006

- [11] Ahmed Nader Mohieldin, Edgar Sanchez-Sinencio, Jose Silva-Martinez, "Nonlinear Effects in Pseudo Differential OTAs With CMFB," *IEEE Trans Circuits Syst.*, vol. 50, no. 10, Oct. 2003

- [12] Ko-Chi Kuo, Adrian Leuciuc, "A Linear MOS Transconductor Using Source Degeneration and Adaptive Biasing," *IEEE Trans Circuits Syst*, vol. 48, no. 10, Oct. 2001

- [13] Wenchang Huang, Edgar Sanchez-Sinencio, "Robust Highly Linear High-Frequency CMOS OTA With IM3 Below -70 dB at 26 MHz," *IEEE Trans Circuits Syst.*, vol. 53, no. 7, Jul. 2006.

- [14] Jianlong Chen, Edgar Sanchez-Sinencio, Jose Silva-Martinez, "Frequency-Dependent Harmonic-Distortion Analysis of a Linearized Cross-Coupled CMOS OTA and its Application to OTA-C Filters," *IEEE Trans Circuits Syst.*, vol. 53, no. 3, Mar. 2006.

- [15] Artur J. Lewinski, Jose Silva-Martinez, "A 30-MHz Fifth-Order Elliptic Low-Pass CMOS Filter With 65-dB Spurious-Free Dynam Range, *IEEE Trans Circuits Syst*, vol. 54, no. 3, Mar. 2007

- [16] Zhenhua Wang, Walter Guggenbuhl, "A Voltage-Controllable Linear MOS Transconductor Using Bias Offset Technique," *IEEE J. Solid-State Circuits*, vol. 25, no. 1, Feb. 1990

- [17] Ramirez-Angulo J., Balasubramanian S., Lopez-Martin A.J., Carvajal R.G, "Low Voltage Differential Input Stage With Improved CMRR and True Rail-to-Rail Common Mode Input Range," *IEEE Trans. Circuits Syst.* II, Exp. Briefs, vol. 55, no 12, pp. 1229 – 1233, Dec 2008.

#### **AUTHORS**

First Author – Reetesh V. Golhar, M.Tech persuing, BDCE Sevagram, Maharashtra, India, reetesh.golhar@gmail.com Second Author – Mahendra A. Gaikwad, PhD, BDCE Sevagram, Maharashtra, India, gaikma@rediffmail.com Third Author – Vrushali G. Nasre, PhD persuing, BDCE Sevagram, Maharashtra, India, vrushnasre@gmail.com