# **Design of Mimo Detector using K-Best Algorithm**

## Akila. V, Jayaraj. P

Assistant Professors, Department of ECE, Surya Engineering College, Erode-638107.

**Abstract-** This paper presents an efficient VLSI architecture for a 4x4 64-QAM multiple-input–multiple-output (MIMO) detector. The augmentation is done by on demand expansion of intermediate nodes of the tree rather than exhaustively, along with pipelined distributed sorters. The proposed architecture has a stable critical path independent of constellation size, scalable to higher number of antennas with efficient distributed sorters. Further, modification will be carried out with the faster multiplication unit to make it scalable to higher number of antennas.

*Index Terms*- K-best algorithm, multiple-input-multiple-output (MIMO), on-demand expansion.

#### I. INTRODUCTION

Multiple-input-multiple-output (MIMO) systems have gained significant concentration as the hand-picked technology in many standards such as IEEE 802.11n, IEEE 802.16e, IEEE 802.16m and the long term evolution (LTE) paper due to the high spectral efficiency. To accomplish the potential of MIMO systems, the main challenge is to design high throughput detection device of low complexity with near maximum-likelihood (ML) performance that are suitable for efficient very large scale integration (VLSI) implementation. Unluckily, with the number of transmit antennas and the constellation size the complexity of the optimal ML detection scheme grows exponentially. Available lower-complexity detectors such as zero-forcing (ZF), minimum mean-square error (MMSE) or successive interference cancelation (SIC) detectors can greatly reduce the computational complexity but still they go through performance loss.

The other choice is to use near-optimal non-linear detectors. Near-optimal non-linear detectors can be classified as depth-first search, breadth-first search, and best-first search based on nonexhaustive search. Depth-first sphere decoding (SD) have drawn attention in depth-first approach whose performance is optimal under the assumption of unlimited execution time. However, the actual runtime of the algorithm not only accounts for the channel realization but also depends on the operating signal-to-noise-ratio (SNR). Thus obtaining a variable sustained throughput, which results in extra overhead in the hardware due to the extra required I/O buffers and lower hardware utilization.

Among the breadth-first search methods, the familiar approach is the K-best algorithm. The K-best detector assures fixed-throughput with a performance close to ML which is independent of SNR. Being fixed-throughput in nature along with the fact that the breadth-first approaches are feed-forward detection schemes, makes them especially attractive for VLSI implementation. Moreover, in spite of various published architectures for the implementation of  $4\times4$  16-QAM systems, an efficient high-throughput application specific integrated circuit (ASIC) implementation for 64-QAM systems at high data rate is still a major challenge and has not been fully addressed in the literature.

In this paper, an efficient VLSI architecture is designed for a  $4\times4$  64-QAM *K*-best MIMO detector, which lessen the problems described above and operates at a significantly higher throughput. It efficiently expands all the possible children and provides K-best solution.

## II. K-BEST ALGORITHM

A spatial multiplexing MIMO system is considered with N<sub>t</sub> transmit and N<sub>r</sub> receive antennas whose equivalent baseband model of the Rayleigh fading channel described by a complexvalued N<sub>r</sub> x N<sub>t</sub> channel matrix  $\hat{\mathbf{H}}$ . The complex baseband equivalent model can be expressed as  $\tilde{\mathbf{y}} = \hat{\mathbf{H}}\tilde{\mathbf{s}} + \tilde{\mathbf{v}}$  where  $\tilde{\mathbf{s}} = [\tilde{\mathbf{s}_1}, \tilde{\mathbf{s}_2}, \dots, \tilde{\mathbf{s}_{N_t}}]^T$  denotes the N<sub>t</sub>-dimensional complex transmit signal vector, in which each element is independently drawn from a complex constellation O (a symmetric *M*-QAM scheme with  $\log_2 M$  bits per symbol, i.e., |O| = M),  $\tilde{\mathbf{y}} = [\hat{\mathbf{y}}_1, \hat{\mathbf{y}}_2, \dots, \hat{\mathbf{y}}_{N_T}]^T$  is the N<sub>r</sub> –dimensional received symbol vector, and  $\tilde{\mathbf{v}} = [\tilde{\mathbf{v}}_1, \tilde{\mathbf{v}}_2, \dots, \tilde{\mathbf{v}}_{N_T}]^T$  represents the N<sub>r</sub> - dimensional independent identically distributed complex zero-mean Gaussian noise vector with variance  $\sigma^2$ , i.e.,  $\tilde{\mathbf{v}}_i \sim N_c(0, \sigma^2)$ . The real model can be derived equivalent to this system using a real-valued decomposition (RVD) model as follows:

$$y=Hs+v$$

(1)

where  $y=[y_1, y_2, ..., y_{2Nr-l_i}, y_{2N_r}]^T$ ,  $s=[s_1, s_2, ..., s_{2Nt-l_i}, s_{2N_t}]^T$ and **H** are the equivalent real-valued vectors with the following mappings  $y_{2k-1} = \Re\{\widetilde{y_k}\}$ ,  $y_{2k} = \Im\{\widetilde{y_k}\}$ ,  $s_{2k} = \Im\{\widetilde{y_k}\}$ , and **v** and **H** are decomposed accordingly, where  $\Re(..)$  and  $\Im(..)$  denote the real and imaginary parts of the variables, respectively. Note that  $s_i \in \Omega_{=\{-\sqrt{M}+1, ..., -1, +1, ..., +\sqrt{M}+1\}}$ , where  $\Omega$  is the set of possible real entries in the constellation for in-phase and quadrature parts with  $|\Omega| = \sqrt{M}$ . The aim of the MIMO ML detection method is to find the closest transmitted vector  $\hat{s}$ based on the observation , i.e.,

$$\hat{\mathbf{s}} = \arg \min_{\boldsymbol{s} \in \Omega^{2N_t}} \left| \left| \mathbf{y} - \mathbf{H} \mathbf{s} \right| \right|^2 \qquad (2)$$

The exhaustive-search ML detection is not effective to implement for large constellation sizes (i.e., 64-QAM and larger) because of its exponential complexity nature. The *K*-best

algorithm, a.k.a. the M-algorithm, is a near-ML technique to solve the above problem with a much lower complexity.

The problem in (2) can be considered as a tree-search problem with  $2N_t$  levels. The *K*-best algorithm explores the tree from the root to the leaves by expanding each level and it selects the best candidates with the lowest PED in each level that are the surviving nodes of that level. Consider the problem in (2), and let us denote the QR-decomposition of the channel matrix as  $\mathbf{H}=\mathbf{QR}$ , where  $\mathbf{Q}$  is a unitary matrix of size  $2N_r \times 2N_t$  and  $\mathbf{R}$  is an upper triangular  $2N_t \times 2N_t$  matrix. Applying  $\mathbf{Q}^{\mathbf{H}}$  to (1) results in

$$\mathbf{Z} = \mathbf{Q}^{\mathrm{H}}\mathbf{y} = \mathbf{R}\mathbf{s} + \mathbf{w} \tag{3}$$

where  $\mathbf{w} = \mathbf{Q}^{\mathbf{H}} \mathbf{v}$ . Since the nulling matrix is unitary, the noise,  $\mathbf{w}$ , remains spatially white and the norm vector in (2), which represents the ML detection rule, can be rewritten as  $\hat{\mathbf{s}} = \arg \min_{\mathbf{s} \in \Omega^{2N_t}} ||\mathbf{z} - \mathbf{Rs}||^2$ . Exploiting the upper triangular nature of **R**, this norm vector can be further expanded as

$$\hat{s} = \arg \min_{s \in \Omega^{2N_t}} \sum_{l=1}^{2N_t} z_l - \sum_{j=l}^{2N_t} \eta_j s_j \mid^2 \quad (4)$$

## TABLE I K-BEST ALGORITHM

**Step 1) Initialization:** Set one path at level  $2N_t+1$  with PED=0 **Step 2) Expansion:** Expand K surviving paths from the last level

to  $\sqrt{M}$  new children in  $\Omega$  & calculate the PED of new  $K\sqrt{M}$  paths.

**Step 3**) **Sorting:** Sort all  $K^{\sqrt{M}}$  existing paths PED and select the best K paths.

**Step 4**) If not at the last level, go to step 2, o.w. announce the path with the lowest PED.

which is a tree-search problem with levels. Starting from  $l = 2N_t$ , (4) can be evaluated recursively as follows:

$$T_{l}(s^{(l)}) = T_{l+l}(s^{(l+1)}) + |e_{l}(s^{(l)})|^{2}$$

$$e_{l}(s^{(l)}) = z_{l} - \sum_{j=l}^{2N_{t}} \eta_{j} s_{j} = L_{l}(s^{(l)}) - \eta_{l} s_{l}$$

(6)

for  $l = 2N_t, 2N_t - 1, ..., 0$ , where  $s^{(l)} = [s_l s_{l+1} ... s_{2N_t}]^T$ ,  $T_l(s^{(l)})$ is the accumulated partial Euclidean distance (PED) with  $T_{2N_t+1}(s^{2N_t+1}) = 0$ ,  $e_l(s^{(l)})^2$  denotes the distance increment between two successive nodes/levels in the tree, and

$$L_{l}(S^{(l)}) = z_{l} - \sum_{j=l+1}^{2N_{t}} \eta_{j} s_{j} = \eta_{l} (\overline{z_{l}} - \sum_{j=l+1}^{2N_{t}} \overline{\eta_{j}} s_{j})$$

=  $\eta_{l} \overline{L_{l}}(s^{(l)})$  (7)

where  $\overline{z_l}$ ,  $\overline{\eta_j}$ , and  $\overline{L_l}(s^{(l)})$  denote the scaled  $z_l$ ,  $\eta_j$ , and  $L_l(S^{(l)})$  by  $\eta_l$ , respectively, i.e.,  $z_l = \overline{z_l} \eta_l$ ,  $\eta_j = \overline{\eta_j} \eta_l$ , and  $\overline{L_l}(s^{(l)}) = L_l(S^{(l)}) \eta_l$ . Based on the above formulation, the *K*-best algorithm can be described as in Table 1.

The path with the lowest PED at the last level of the tree is the hard-decision output of the detector, whereas, for a softdecision output, all of the existing paths at the last level are considered to calculate the Log-Likelihood Ratios (LLRs)

Let us consider a  $2N_r \times 2N_t$  real-model MIMO system with channel matrix **H**(1). The system is considered as a detection problem in a tree with  $2N_t$  levels, **K** nodes per level and  $\sqrt{M}$  children per node. The algorithm starts from the last row of the matrix because of the upper triangular structure of matrix **R** and goes all the way up to the first level of the detection tree.

There are two main computations that take major roles in the total computational complexity of the algorithm, namely, 1) the expansion of the surviving paths, and 2) the sorting. Therefore, for VLSI realization of the K-best algorithm these two computational cores are considered as most important one.

1) Expansion: Efficient expansion method called the *on-demand* expansion scheme is carried out, which avoids the exhaustive enumeration of the children and obtain exact *K*-best implementation with no performance loss. There are *K* parent nodes at each level and  $\sqrt{M}$  children per parent, thus the path metrics of  $K\sqrt{M}$  children is to be computed in each level, which leads to a large computational complexity. The computational complexity is independent of constellation size and proportional to the *K* value.

2) *Sorting:* In this paper, a distributed sorter, working in a pipelined structure based on the on-demand expansion scheme is considered.

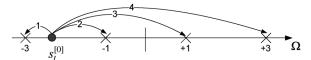

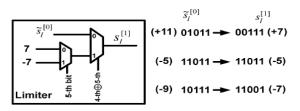

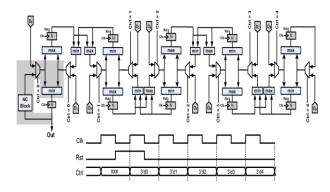

Figure 1: Order of the SE row-enumeration for four consecutive enumerations in 16-QAM

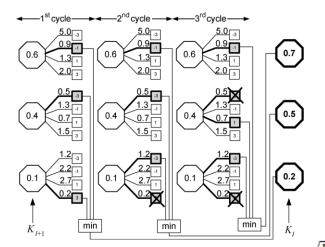

It obtains K best candidates in K clock cycles. It is applicable for any value of K and M.

#### III. PROPOSED K-BEST DETECTION SCHEME

Consider level of the tree and assume that the set of *K*-best candidates in level l+1 (denoted by  $K_{l+1}$ ) is known. Each node in level has possible children, so there are possible children in level *l*. The *K*-best scheme is used to find the first child (FC) of each parent node in  $K_{1+1}$ . Among these first children the one with the lowest PED is one of the *K*-best candidates in  $K_l$  for sure. That specific child is taken and replaced by its next best sibling. This process repeats *K* times to find the *K*-best candidates in level *l* ( $K_l$ ). The same approach is used at each level.

#### A. First/Next Child Calculation

In the on-demand scheme described above, the *first* and *next* child are required to be determined. Based on the system model

in (5), the first child  $(s_l^{[1]})$  of a node in  $K_{l+1}$  is the one minimizing  $e_l(s^{(D)})$ , i.e.,

$$s_{l}^{[1]} = \arg\min_{s \in \Omega^{2N_{t}}} e_{l} (s^{(l)})^{2} = \arg\min_{s \in \Omega^{2N_{t}}} L_{l} (s^{(l)}) - \eta_{l} s_{l}^{2}) (8)$$

Therefore,  $s_l^{[1]}$  can be found by rounding  $s_l^{[0]} = L_l(s^{(1)})/\eta_l$ to the nearest integer value in  $\Omega$ . In order to find the next children (NC), the Schnorr-Euchner technique is employed, which implies a zig-zag movement around  $s_l^{[0]}$  to select the consecutive elements in  $\Omega$ . Figure. 1 shows such an enumeration for  $\sqrt{M} = 4$ . The SE enumeration by changing the search direction finds the closest points in a real domain one-by-one. The procedure is described in Table II, where n/ denotes the number of moves, and **SignBit** represents the direction. **SignBit** alternates between positive and negative until it reaches  $\pm \sqrt{M} - 1$ . The number of moves also increases by 2 every time and is reset to 2 if boundaries of  $\Omega$  are reached.

## TABLE II

First/Next child selection procedure for node j

A) First child A.1)  $s_l^{[0]} = L_l(s^{(l)})/r_{ll}$ A.2)  $s_l^{[1]\leftarrow}$ ,  $n_l^{i\leftarrow} 2$ B) Next (k-th) child  $\begin{cases}

SB & s_l^{[k-1]} \neq \pm(\sqrt{M} - 1) \\

-1 & s_l^{[k-1]} = (\sqrt{M} - 1) \\

+1 & s_l^{[k-1]} = -(\sqrt{M} - 1) \\

where SB=Sign(s_l^{[k-1]} - s_l^{[k-2]}) \\

B.2) s_l^{[k]\leftarrow} s_l^{[k-1]} + n_l^{j} \times \text{SignBit.} \\

\begin{cases}

2 & \text{if } s_l^{[k-1]} = \pm(\sqrt{M} - 1) \\

y = \pm(\sqrt{M} - 1) \\

y = \pm(\sqrt{M} - 1) \\

y = \pm(\sqrt{M} - 1)

\end{cases}$

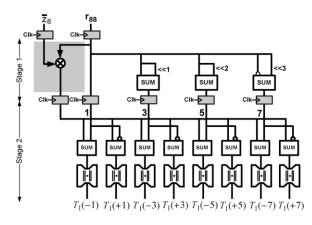

Figure 2: The proposed distributed *K*-best algorithm for  $\sqrt{M}$ = 4 and *K*=3 and example PED values.

#### IV. VLSI IMPLEMENTATION

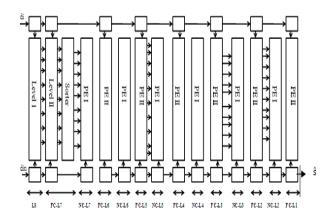

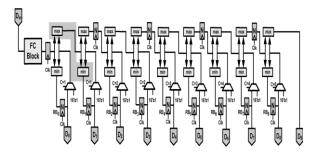

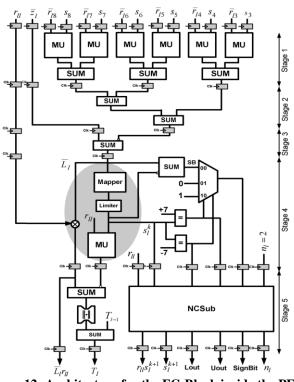

A pipelined structure is used, which performs the child expansion and minimization jointly in a pipelined fashion and implements the sorting in a distributed way without sacrificing the throughput. The proposed architecture with all intermediate parameters for a 4×4, 64-QAM MIMO system with K=10 and  $\Omega=\{-7,-5,-3,-1,+1,+3,+5,+7\}$  is shown in Figure. 3. There are  $2N_{r}=8$  levels in the tree. The 8th level of the tree, corresponding to the last row of (3), opens up all the possible values in  $\Omega$ , and calculates their corresponding PEDs.

Figure 3: Proposed pipelined VLSI architecture of the K-best algorithm for the detection of a  $4 \times 4$ , 64-QAM system with K=10

The output of this stage is  $|\Omega|=8$  PED values which is performed by Level I. First child is found and its PED is updated using the FC-Block in Level II. Then the FC with the lowest PED should be determined, which requires all the FCs to be sorted. This is done using the Sorter block. The output of the Sorter block is the sorted FCs of level 7 are loaded simultaneously to the next stage PE II block is used to generate and sort the list of all FCs of the current level and 1 PE I block is used to generate the *K*-best list of the current level to the next stage.

## V. DETAILED VLSI ARCHITECTURE

The inputs to the architecture are the entries of the matrix as well as z the vector in (3). The basic blocks used throughout the architecture discussed as follows.

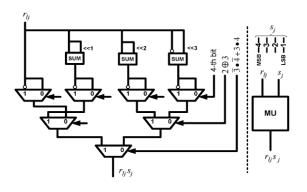

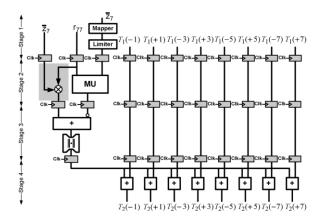

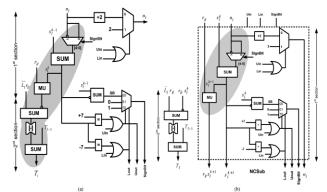

**Multiplication (MU):** Two types of multiplication carried out in the architecture. The multiplication of  $\overline{z_l} \times \eta_l$  and  $s_j \times \overline{\eta_j}$ . The former multiplication implemented using a 13 bit × 13 bit multiplier. The later carried out with a faster multiplication unit consuming less area shown in Figure.4

Figure 4: Alternative architecture for multiplication (MU).

**Mapper:** once  $s_l^{[0]}$  is calculated as given in Table II, then by mapping it to the nearest odd integer in  $\Omega$  first child is calculated which is carried out in two consecutive stages as shown.

**Limiter:** If  $\overline{s_l^{[0]}}$  exceeds the boundaries of  $\Omega$ , the limiter block is used to bound the values with in upper and lower range of  $\Omega$  (e.g., +7/-7 for 64-QAM). The limiter block is shown in Figure. 5, with examples to determine first child for 3 values.

Figure 5: Architecture for the Limiter block.

Figure 6: Architecture for Level I.

1) Level I Block: The nodes in the 8<sup>th</sup> level of tree are taken as input to the Level I and corresponding PED values are generated as output. The architecture shown in Figure. 6 involves 13 bit  $\times$  13 bit multiplier, adder and absolute value block. Absolute value block may represent either  $l^{l}$  norm or  $l^{2}$  norm. Former can be replaced with squaring operation and later can be replaced with carry save adder technique. Fine grained pipelining is introduced in this block to increase the system throughput. 2 stage pipelining is employed here shown by the introduction of 2 and 5 positive-edge-triggered flip-flops in stage 1 and 2 respectively. Resulting in avoidance of long critical path assuming that there is only one multiplication unit in the critical path.

2) Level II Block: The PED values of the 8<sup>th</sup> level are given as input to the Level II block and PED values of first children in 7<sup>th</sup> level are generated as output. The first children of the 7<sup>th</sup> level are same and independent of 8<sup>th</sup> level of the tree due to the structure of the **R** matrix. To find first child  $\overline{z_7}$  is applied to the limiter/mapper block and it is multiplied with  $r_{777}$  by using MU block. Normalized input  $\overline{z_7}$  is also multiplied with  $r_{777}$ . The Euclidean distance between the first child and received vector is calculated and it is added with PED values of 8<sup>th</sup> level, resulting in updated 8 PED values of 7<sup>th</sup> level. 4-stage pipelining is introduced to reduce the length of critical path as shown in Figure. 7.

Figure 7: Architecture for Level II.

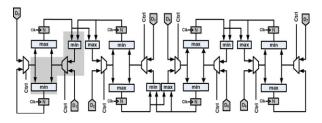

3) Sorter Block: The updated PED values of  $7^{th}$  level FC's are given as input to the sorter block to generate sorted list of these 8 PED values. Eight inputs are denoted as  $D_0$ - $D_7$  loaded with the **ctrl** signal and the outputs are stored in flip-flop denoted as "N" as shown in Figure. 8. The general sorter involves two operations in one clock cycle (min/max and data exchange) sorts **K** numbers in **K/2** clock cycles.

4) PE I Block: PE I is a common block shown in Figure. 9 used from level 7 to level 2. The sorted list of first children of each level is received and it generates **K**-best candidates of that level. For example in level 7 the output of PE I, called NC-L7 consists of lowest PED values generated one-by-one at the output in series. This block composed of a sorter, and a block called NC-Block on the feedback path. Sorted list of PEDs received from the preceding stage and selects best one with lowest PED, and it is taken as K-best candidate. NC-Block then calculates the next best sibling of that candidate and fed it back to the sorter to find the location of the new sibling that present already in the sorted list. Efficient architecture to be considered for NC-Block since it is present in the critical path.

Figure 8: Architecture for the Sorter block.

Figure 9: Architecture for the PE I block.

Figure 10: Architecture for the NC-Block inside the PE I block (a) Original. (b) Improved.

5) NC-Block: The NC-Block shown in Figure. 10 involves three operations. SignBit calculates the direction of the SE enumeration for the next child, check for lower/upper boundary in  $\Omega$  and finally calculates the PED value of new sibling. To obtain a efficient architecture the following two methods are used in VLSI architecture:

1)Avoid multiplication: Since the value of  $L_{I}$  in (7) independent of current sibling and it depends only on the selected symbols till level *l*. The calculation of  $\overline{L}_{I}$  and  $\overline{L}_{I} r_{ll}$  can be done by FC-Block in the preceding stage and it is moved as input to the NC-Block. This is the preferred technique that removes the multiplication from the critical path.

2)Broken critical path: The critical path is broken down in to two smaller parts. As can be seen from the Figure. 10(a), the original structure has 3 adders along with the MU unit. Using scheduling method, the first part of the critical path calculates the next sibling and further it is moved to the FC-Block in the preceding block as shown in Figure. 10(b). For each it calculates both the first and second best child and it sends to the NC-Block. The NC-Block calculates the second best child while determining the third child and it goes on. This obviously shows that NC-Block always calculates one child ahead. The first section calculates the second best child is added to the preceding FC-Block. The second section consists of two adders whose complexity independent of K value.

Figure 11: Architecture for the PE II block.

6) PE II Block: As each of the K-best candidates are found, it is transferred to the PE II block to calculate the first children of next level and sort them. The architecture of PE II block is shown in Figure. 11., where D<sub>in</sub> served as input to generate output namely D<sub>0</sub>-D<sub>9</sub>. At first, FC-Block calculates the first child of K-best candidate and its PED values are updated. To sort these PED values, it is followed by a sequential sorter. PE II block is connected to the output of PE I bock in a pipelined fashion hence the process is carried out on the basis of clock cycles. Two register banks are updated at the same time in every clock cycle. 7) FC-Block: The main assignment of this block is to calculate  $L_{l}$ in (7). Based on this  $\overline{L}_{l}$  value, the first child of current parent node and its PED values are calculated. Pipelining has been used by the introduction of FFs on all the forward paths. The proposed architecture for the FC-Block consists of 5 pipeline levels. In first two levels  $\sum_{j=l+1}^{2N_t} \eta_j s_j$  is calculated.  $\overline{L}_l$  is calculated in third level, which is used to find first child using mapper and limiter bock. The next best child needed for NC-Block is determined by finding the number of moves and direction of moves for the SE enumeration. Finally the PED value of announced first child is calculated in the level 5 as shown in Figure. 12.

Figure 12: Architecture for the FC-Block inside the PE II block.

### VI. RESULT ANALYSIS

#### A) Simulated waveform

| <u>ه</u> -             | Maga                                    |                                         |

|------------------------|-----------------------------------------|-----------------------------------------|

| 🌢 /top_module/dk       | St1                                     |                                         |

| 1 /top_module/rst      | SHD                                     |                                         |

| D-4 /top_module/28     | 100100100100                            | 1001001000100                           |

| D / top_module/27      | 0 100 10 1 10000 1                      | 0100101100001                           |

| T-1 /top_module/r8     | 1001011111100                           | 1001011111100                           |

| D-1 /top_module.h7     | 1010101011110                           | 1010101011110                           |

| D-1/ /top_module/d0    | 000000000000000000000000000000000000000 | 202000000000000                         |

| D-1/20_module/d1       | 00000000000000000                       | 200000000000000                         |

| D-1/100_module/82      | 0000000000000000000                     | 200000000000000                         |

| 0-1/10p_module/d3      | 000000000000000000                      | 200000000000000                         |

| D-1/100_module/64      | 000000000000000000                      | 200000000000000                         |

| D-1/100_module/d5      | 00000000000000000                       | 200000000000000                         |

| 0-4 /top_module.id6    | 00000000000000000                       | 200000000000000                         |

| D-1/20_module/07       | 00000000000000000                       | 20000000000000                          |

| D-1/20_module/d8       | 00000000000000000                       | 000000000000000000000000000000000000000 |

| 🗗 👍 /tap_module/d9     | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |

| 🗗 🥠 /top_module/pe2_in | 0011000011000                           | 0011000011000                           |

| E-\$ /top_module.jp1   | 1000010011030                           | 2000000000000000 200000000000 2000      |

| D-1/ hop_module.jp2    | 1000010011000                           | 2000000000000000 [20000000000 [2000     |

| D-4 /top_module.jp3    | 1000010011010                           | 2000000000000000 200000000000 2000      |

| 🗗 🔶 /top_module.jp4    | 1000010011000                           | 2000\$000000\$0000 [200000\$0000 [2000  |

| C-+/ /top_module.jp5   | 1000010011010                           | 200000000000000000000000000000000000000 |

| D- / (ap_module.jp6    | 1000010011000                           | 20004000000000000 200000000000 2000     |

| D-1/100_module.107     | 2000010012001                           | 200000000000000000000000000000000000000 |

| 🖸 🥠 /top_module.jp8    | 1000010011001                           | 2000000000000000 20000000000 2000       |

| D-/top_module/s1       | 0001010110001                           | 000000000000000000000000000000000000000 |

| Sources X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rst_IBUF_5(rst_I                                                                                             | BUF_5:0)                                                  | NONE(pe4_01/nr6/tmp_25  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------|--|

| Sources for: Synthesis/Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ]                                                                                                            |                                                           | +                       |  |

| 🗐 m5_fc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Tining Comments                                                                                              |                                                           |                         |  |

| 🗄 🕼 xc3s5000-4fg900                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Timing Summary:                                                                                              |                                                           |                         |  |

| B V at top_module (F:/source_code/top_module.v)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Speed Grade: -4                                                                                              |                                                           |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Minimum period: 21.656ns (Maximum Frequency: 46.177MHz)<br>Minimum input arrival time before clock: 22.888ns |                                                           |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |                                                           |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maximum output required time after clock: 14.421ns                                                           |                                                           |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maximum combi:                                                                                               | national path del                                         | ay: 17.980ns            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Timing Detail:                                                                                               |                                                           |                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |                                                           |                         |  |

| ()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | All values displayed in nanoseconds (ns)                                                                     |                                                           |                         |  |

| 🕰 Sources 👩 Snapshots 🚺 Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |                                                           |                         |  |

| Processes X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Timing constrain                                                                                             | analysis for Clock 'clk'                                  |                         |  |

| Processes for: top_module^                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock period: 21.656ns (frequency: 46.177MHz)                                                                |                                                           |                         |  |

| ter 🏉 Design Unities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Total number of                                                                                              | Total number of paths / destination ports: 8482985 / 3024 |                         |  |

| E 🎽 User Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |                                                           |                         |  |

| Contraction of the second seco | Delay:                                                                                                       |                                                           | vels of Logic = 14)     |  |

| Wew Synthesis Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Source:                                                                                                      | pee_02/ICu/d                                              | ff_aop11/temp_10_2 (FF) |  |

The best child with lowest PED value is found as shown in the simulated waveform. Array multiplier unit involved in this structure obtaining delay of 21.656 ns, throughput of 46.177 MHz carried out in XILINX ISE 9.1i.

#### VII. CONCLUSION AND FUTURE WORK

The efficient pipelined architecture is simulated with reduced delay achieving low data rate. It supports for any value of K and M thus scalable to higher number of antennas. Further, modifications can be done with multiplication unit by using fast multiplier techniques involved in Vedic mathematics to improve the throughput and reduce the delay.

#### REFERENCES

- "A 675 Mbps, 4 x 4 64-QAM K-Best MIMO Detector in 0.13 μm CMOS" Mahdi Shabany and P. Glenn Gulak, IEEE Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 20, No. 1, January 2012

- [2] Chung-An Shen And Ahmed M. Eltawil,(2010) "A Radius Adaptive K-Best Decoder With Early Termination: Algorithm And VLSI Architecture", IEEE Transactions On Circuits And System-I: Regular Papers, Vol. 57, No. 9.

- [3] Chen S and Zhang T, (2007) "Low power soft-output signal detector design for wireless MIMO communication systems," in Proc. Int. Symp. Low Power Electron. Design, pp. 232–237.

- [4] Chen S, Zhang T, and Xin Y,(2007) "Relaxed K-best MIMO signal detector design and VLSI implementation," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 3, pp. 328–337.

- [5] Li Q and Wang Z,(2006) "An improved K-best sphere decoding architecture for MIMO systems," in 40th Asilomar Conf. Signals, Syst. Comput., pp. 2190–2194.

- [6] Guo Z and Nilsson P,(2006) "Algorithm and implementation of the K-best sphere decoding for MIMO detection," IEEE J. Sel. Areas Commun.,vol. 24, no. 3, pp. 491–503.

#### AUTHORS

**First Author** – Akila. V, Assistant Professors, Department of ECE, Surya Engineering College, Erode-638107., Email: vakilavenkatachalam@gmail.com

**Second Author** – Jayaraj. P, Assistant Professors, Department of j ECE, Surya Engineering College, Erode-638107., Email:

jayece015@gmail.com